# Enhanced Subthreshold Slopes in Large Diameter Single Wall Carbon Nanotube Field Effect Transistors

Simone Pisana, *Student Member, IEEE*, Can Zhang, Caterina Ducati, Stephan Hofmann, and John Robertson, *Member, IEEE*

Abstract—The performance of single wall carbon nanotube field effect transistors (SWNT FETs) is greatly affected by the quality of its contacts. The presence of Schottky barriers imposes a strong scaling of the gate dielectric thickness. Here, we employ large diameter SWNTs in order to fabricate ohmically contacted FETs when a lower work function but higher adhesion strength metal such as Cr is used. A subthreshold slope as low as 113 mV/dec is obtained even when employing a thick, 200 nm  $\rm SiO_2$  dielectric. The result is examined in light of the positive effects of exposure to air and underlines the possibility for less stringent device fabrication techniques.

Index Terms—Field effect transistor (FET), ohmic contact, Schottky barrier, single wall carbon nanotube (SWNT).

## I. INTRODUCTION

HE PERFORMANCE of field effect transistors (FETs) based on single well seed on single well seed to be a single well seed based on single wall carbon nanotubes (SWNTs) has been studied for several years, owing to their potential for novel transistor technologies based on nanomaterials [1]-[3]. It is now accepted that FETs fabricated with semiconducting SWNTs feature varying performance, depending mainly on the quality of the contacts at the nanotube-electrode interface, the type and thickness of the gate dielectric, and length of the channel [4]–[12]. An important performance parameter is the subthreshold slope (S), which determines the variation in gate voltage required to switch a transistor between its high and low conductance states. A low subthreshold slope is desirable in complementary logic, as it increases the switching speed and lowers the power consumption. It has been shown that SWNT FETs having Schottky barriers at the nanotube-electrode interface (SB-FETs) have an undesirable subthreshold performance [4], [6], [7], since the gate electric field's function is to modulate the Schottky barrier height and thereby modulating the barrier's screening length and tunneling probability. In this case, the subthreshold slope of SB-FETs can be improved by drastically lowering the gate oxide thickness and/or

Manuscript received August 15, 2007; revised October 11, 2007. This work was supported by the EU project CAlcul Numérique sur Architecture ProgrammablE (CANAPE). The works of C. Ducati and S. Hofmann was supported by The Royal Society. The work of S. Hofmann was also supported by Peterhouse, Cambridge. The review of this paper was arranged by Associate Editor J. Rogers.

S. Pisana, C. Zhang, S. Hofmann, and J. Robertson are with the Engineering Department, University of Cambridge, Cambridge CB3 0FA, U.K. (e-mail: sp406@cam.ac.uk).

C. Ducati is with the Department of Materials Science and Metallurgy, University of Cambridge, Cambridge CB2 3QZ, U.K.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNANO.2008.917849

<sup>1</sup>Provided that the threshold voltage and its variation between devices is low as well.

using higher dielectric constant gate oxides in order to increase the gate capacitive coupling. On the other hand, ohmically contacted SWNT FETs behave similarly to standard MOSFETs (NT-MOSFETs) [4], [8], [13], where the gate electric field directly affects the carrier concentration in the channel. In NT-MOSFETs, S can potentially reach the room-temperature theoretical limit of  $\sim\!60$  mV/dec without relying as heavily on thin, high dielectric constant gate oxide layers [4]. NT-MOSFET operation is hence desirable over SB-FETs because it allows for less challenging device fabrication techniques in order to obtain comparable transfer performance.

In this paper, we present NT-MOSFETs fabricated using larger diameter SWNTs in order to form low barrier contacts to Cr, which is know for its high adhesion strength. Aging in air is shown to further reduce the barrier, which is found to be negligible by performing measurements at low temperatures. The results show that this technique can be used to obtain NT-FETs that have improved subthreshold switching performance without employing thin or high dielectric constant gate dielectrics. This can relax the fabrication requirements for inexpensive or large scale devices and sensors based on SWNTs.

#### II. EXPERIMENTAL

Semiconducting SWNTs feature a band gap with pronounced diameter dependence  $(E_g \sim d^{-1})$  [14], [15]. Here, SWNTs were grown from horse spleen ferritin catalyst, yielding a diameter distribution with a larger mean diameter [16] than conventional HiPCo [17], CoMoCat [18], or laser ablation SWNTs [19]. Ferritin is an iron storage protein consisting of a proteic shell with a hollow core having an inner diameter of  $\sim$ 8 nm filled with hydrous ferric oxide  $(\text{Fe}_2\text{O}_3\cdot 0.5\text{H}_2\text{O})$  [16]. Calcination in air is used to remove the outside proteic shell. Reducing the particles at high temperature in an hydrogen atmosphere can therefore reduce the volume of the nanoparticles by at least 90%, yielding Fe nanoparticles with a small diameter distribution centered at  $\sim$ 3.5 nm.

The SWNTs were grown by chemical vapor deposition in a 2-in diameter quartz tube furnace, operated at atmospheric pressure. The as-received ferritin (Sigma–Aldrich) was diluted in deionized (DI) water (1:400 v/v), a drop was placed on the substrate and spun dry at 5000 r/min. The substrates used were degenerately n doped crystalline Si wafers, used as a back gate electrode, covered with a 200-nm thick thermally grown SiO<sub>2</sub> layer, which acts as a gate dielectric. The ferritin deposited on the substrate was calcinated in air at 500 C for 10 min in order to burn the protein shell surrounding the Fe catalyst core. Following this, the substrates were heated in a 1000 sccm Ar

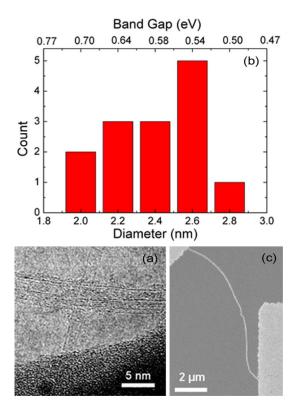

Fig. 1. (a) Typical TEM image of the synthesized SWNTs. (b) Diameter distribution of the SWNTs obtained from TEM imaging and corresponding band gap (obtained from [15]) for semiconducting nanotubes. (c) Typical SEM image of a 10- $\mu$ m long FET device.

flow to a temperature of 900 C. Subsequently, the Ar flow was replaced by a reducing atmosphere of  $H_2$  at 200 sccm for 10 min. Growth took place in 15 min by diminishing the  $H_2$  flow and introducing  $CH_4$  at 100 and 500 sccm, respectively. Finally, the furnace was flushed in a 4000 sccm Ar flow, and the sample was cooled to room temperature in Ar. The resulting SWNTs where imaged in a LEO 1530VP field-emission gun scanning electron microscope (FEG-SEM) and characterized by high resolution transmission electron microscopy (HRTEM) with a Jeol JEM 4000EX operated at 400 kV.

Transmission electron microscopy (TEM) imaging reveals an SWNT diameter distribution centered around ~2.4 nm [see Fig. 1(a) and (b)], which is consistent with the expected Fe nanoparticle loss of volume upon reduction and the reported nanoparticle deformation during SWNT nucleation [20]. The obtained diameter distribution corresponds to typical semiconducting nanotube band gaps of ~0.58 eV, as determined by two-photon excitation spectroscopy [15]. The devices were fabricated by defining source and drain electrodes (3 nm Cr covered by 20 nm Au) via standard electron beam lithography and liftoff [see Fig. 1(c)]. Electrical measurements were performed in air using Keithley 2400 source meter units or in a He refrigerated probe station in vacuum using an HP 4156B parameter analyzer.

#### III. RESULTS

The room temperature electrical performance of representative SWNT devices aged in air for two months are shown in Fig. 2. All gate leakage currents are measured to be below 10 pA,

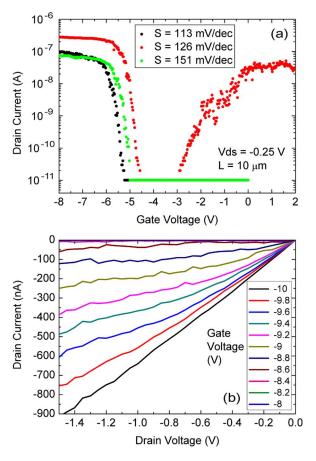

Fig. 2. (a) Transfer curves of different aged SWNT FETs, showing monopolar or bipolar behavior and reduced subthreshold slopes. (b) Output curves of a typical aged SWNT FET, showing ohmic conduction and high currents.

and therefore, do not contribute to the drain currents. The transfer curves [see Fig. 2(a)] feature unipolar, hole-mediated current transport, or bipolar current transport. As shown in Fig. 2(b), the output curves are linear for hole transport (most negative gate voltages) near zero bias, indicating the absence of a significant SB, and hence, the alignment between the Cr metal's Fermi level and the SWNT's valence band. From this, one can infer that bipolar transport is possible when the SWNT's band gap is small enough (larger diameters) to allow electron transport when the nanotube's conduction band is lowered sufficiently (more positive gate voltages). As expected, the electron transport in bipolar devices yields nonlinear output curves (not shown), indicating the presence of SBs between the contact metal and the nanotube's conduction band. The drain current ON/OFF ratios are consistently found to be  $>10^4$ , the value being a lower bound estimate due to limitations in the resolution of the measurement system. The ON currents are high, considering the channel length of 10  $\mu$ m, further indicating the lack of SBs [5].

An important feature of the transfer curves shown in Fig. 2(a), relates to the subthreshold slope,  $S = (d \log I_d/dV_{gs})^{-1}$ , where  $I_{ds}$  is the drain current and  $V_{gs}$  the gate voltage. As indicated, the S obtained for these air-aged SWNT-FETs are routinely measured to be below 200 mV/dec. This is an important result, considering that devices fabricated with similar dielectric thickness usually feature S  $\sim$ 1 V/dec [4], [6]. We will consider next

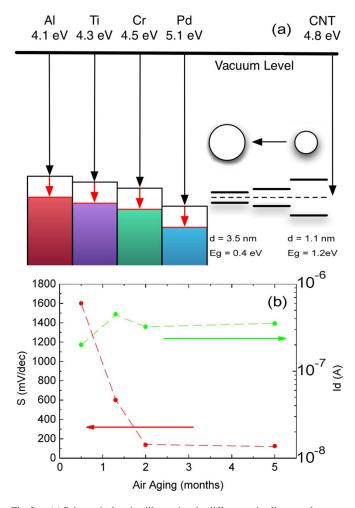

Fig. 3. (a) Schematic drawing illustrating the differences in alignment between valence or conduction band of an SWNT and the Fermi level of various metals. The work function with respect to vacuum level is indicated on top [5], [22]. Different SWNT band gaps (E $_g$ , from [15]) are shown to indicate the effect of the nanotube's diameter (d). Red arrows qualitatively symbolize the increase in work function attributed to exposure to air. (b) Subthreshold slope and ON current (measured at  $V_{ds} = -0.25$  V) as function of aging time in air. The dashed lines guide the eye.

the reasons behind the superior transfer curves obtained and the effects of aging in air.

The barrier height at the nanotube-electrode interface depends mainly on the difference in their work function and on the environment, which can particularly affect the metal work function [7], [13], [21]. Ohmic contacts to typical  $\sim 1.5$  nm diameter (larger band gap) SWNTs are established when using high work function metals such as Pd or Au [8], [13]. These metals, however, suffer from poor adhesion, decreasing the device yield. On the other hand, the diameter dependence of the SWNT's band gap affects the band alignment, potentially allowing for the use of higher adhesion strength, but lower work function metals such as the Cr used here. Fig. 3(a) illustrates the differences in band alignment of SWNTs in contact with several metals. As indicated by the black arrows in the figure, the work functions of bulk metals with better adhesion such as Al, Ti, and Cr, do not provide proper alignment with the valence band of nanotubes of small diameter. In this case, Pd can provide suitable alignment with the valence band, while for conduction band alignment, low work function metals such as Mg and Ca (not shown) are necessary to allow for significant electron-mediated current transport [23]. However, exposure to air can increase the metal's work function with respect to its bulk value due to the adsorption of oxygen, as indicated qualitatively in Fig. 3(a) [7], [21]. It is difficult to quantitatively determine the amount of the work function shift caused by air exposure, as it depends on a number of environmental- and material-dependent factors; however, the general direction of the shift is known, and it may raise or lower with respect to the value of the bulk metal according to the type of molecule adsorbed [7], [13].

Fig. 3(b) shows the dependence of the subthreshold slope and ON current with respect to aging time in air. S has a marked decrease over time from 1.6 V/dec to lower than 200 mV/dec within 2 months, and it is stable afterward. This trend is a good indication that the SB present at the metal-nanotube interface is decreasing as a consequence of exposure to air, converting the SB-FET into an NT-MOSFET [4], [7]. This transition has been observed among different batches of samples; however, the aging time required to stabilize S to a low value varies among batches and can be as short as  $\sim$ 2 weeks. The variation in aging time can be attributed to unintentional surface contamination originating from the device fabrication procedure. The ON current remains fairly stable throughout the process of aging, as shown in Fig. 3(b), excluding the possibility of having oxygen directly doping the SWNTs and being responsible for the changes observed in the subthreshold slope [24].

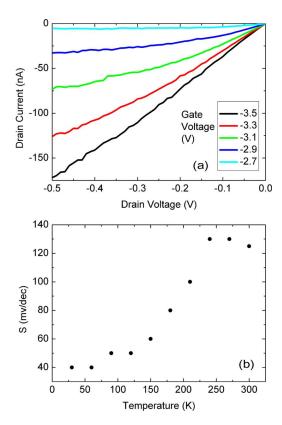

To further investigate the height of the SB in the air-aged NT-MOSFETs, the electrical characterization was performed at low temperature. Fig. 4(a) shows the output curves at 30 K. The curves still show a linear trend near-zero bias, indicating that even at 30 K, the SB is smaller than  $\sim \! 10 \text{ meV}$  [25]. The lack of considerable SB is further confirmed by the temperature trend of S in Fig. 4(b). For SB-FETs, S quickly saturates for decreasing temperatures, indicating the quick decrease in thermally assisted tunneling as the temperature is lowered [4]. Here, instead, there is a marked dependence of S with temperature, similar to what is found in the conventional MOSFETs, where  $S \propto \! 2.3k_BT/e$ , confirming the presence of a negligible SB [13], [26].

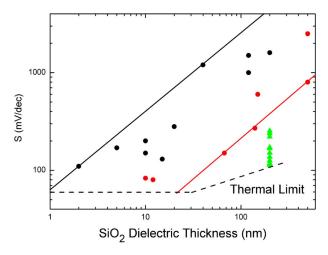

The absence of SBs has been known to improve the subthreshold slope in NT-MOSFETS [4], [26]. To better illustrate this, Fig. 5 compares S obtained for several devices presented in this work (green triangles) with other NT-MOSFETS (red circles) and SB-FETs (black circles), all employing SiO<sub>2</sub> as gate dielectric. All ohmically contacted SWNTs have lower subthreshold slope than the ones having SBs and comparable dielectric thickness. The devices presented here have in the best cases S values approaching the MOSFET thermal limit at 300 K² and are comparable to devices with 3–200 times thinner dielectric, for ohmic or SB contacts, respectively. The improvement in S originates from the larger channel length of the devices used in this work. The shorter the channel, the smaller is the penetration of the electric field between the contacts [7]. The SB-FETs, being more sensitive to the electric field at the metal–nanotube interface, require

<sup>&</sup>lt;sup>2</sup>When an effective dielectric constant of 2.5 is used and no Schottky barriers are present [4].

Fig. 4. (a) Output curves at 30 K, still showing ohmic conduction. (b) Temperature dependence of the subthreshold slope, the behavior is similar to conventional MOSFETS, indicating negligible barrier heights at the electrode–nanotube interface.

Fig. 5. Comparison of subthreshold slopes reported in the literature as function of  $SiO_2$  dielectric thickness. Black circles indicate the presence of Schottky contacts [4], [6], [27]–[29], red circles ohmic contacts [5], [9], [13], [25] [30]–[32], green triangles this work. Black and red lines delimit the highest and lowest values reported and are a guide to the eye. The dashed line indicates the MOSFET thermal limit at 300 K including its variation with oxide thickness [4].

thinner and/or higher dielectric constant gate dielectrics [4]. Therefore, the increased channel length can at least in part account for the low S values reported. The subthreshold performance of the devices presented here have advantages not only in transistor technology, but in applications such as molecular sensing. An ohmically contacted SWNT allows for less strin-

gent device fabrication techniques while maintaining a sharp subthreshold slope, which can drastically improve switching in a transistor or increase the sensitivity of a sensor.

#### IV. CONCLUSION

NT-MOSFETS having low subthreshold slopes were fabricated employing large diameter SWNTs, thereby favoring the formation of ohmic contacts with Cr electrodes. Exposure to air is found to increase the Cr work function, decrease the height of Schottky barriers, and consequently, increase the subthreshold performance. The adoption of a thick gate dielectric and a metal with high adhesion strength allows for less stringent and higher yield fabrication techniques without considerable disadvantages in the device's characteristics.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. D. G. Hasko for valuable discussions.

### REFERENCES

- [1] P. Avouris, J. Appenzeller, R. Martel, and S. Wind, "Carbon nanotube electronics," *P. IEEE*, vol. 91, no. 11, pp. 1772–1784, Nov. 2003.

- [2] A. Graham, G. Duesberg, W. Hoenlein, F. Kreupl, M. Liebau, R. Martin, B. Rajasekharan, W. Pamler, R. Seidel, W. Steinhoegl, and E. Unger, "How do carbon nanotubes fit into the semiconductor roadmap?," *Appl. Phys. A*, vol. 80, no. 6, pp. 1141–1151, 2005.

- [3] M. P. Anantram and F. Leonard, "Physics of carbon nanotube electronic devices," *Rep. Prog. Phys.*, vol. 69, no. 3, pp. 507–561, 2006.

- [4] J. Appenzeller, J. Knoch, V. Derycke, R. Martel, S. Wind, and P. Avouris, "Field-modulated carrier transport in carbon nanotube transistors," *Phys. Rev. Lett.*, vol. 89, no. 12, pp. 126801-1–126801-6, 2002.

- [5] Z. Chen, J. Appenzeller, J. Knoch, Y.-M. Lin, and P. Avouris, "The role of metal-nanotube contact in the performance of carbon nanotube field-effect transistors," *Nano Lett.*, vol. 5, no. 7, pp. 1497–1502, 2005.

- [6] S. Heinze, M. Radosavljevic, J. Tersoff, and P. Avouris, "Unexpected scaling of the performance of carbon nanotube Schottky-barrier transistors," *Phys. Rev. B*, vol. 68, no. 23, pp. 235412–235418, 2003.

- [7] S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller, and P. Avouris, "Carbon nanotubes as Schottky barrier transistors," *Phys. Rev. Lett.*, vol. 89, no. 10, pp. 106801–106804, 2002.

- [8] A. Javey, J. Guo, D. Farmer, Q. Wang, D. Wang, R. Gordon, M. Lundstrom, and H. Dai, "Carbon nanotube field-effect transistors with integrated ohmic contacts and high-k gate dielectrics," *Nano Lett.*, vol. 4, no. 3, pp. 447–450, 2004.

- [9] A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, M. Paul, M. Lundstrom, and H. Dai, "High-k dielectrics for advanced carbon-nanotube transistors and logic gates," *Nat. Mater.*, vol. 1, no. 4, pp. 241–246, 2002.

- [10] B. M. Kim, T. Brintlinger, E. Cobas, M. S. Fuhrer, H. Zheng, Z. Yu, R. Droopad, J. Ramdani, and K. Eisenbeiser, "High-performance carbon nanotube transistors on SrTiO3/Si substrates," *Appl. Phys. Lett.*, vol. 84, no. 11, pp. 1946–1948, 2004.

- [11] Y.-M. Lin, J. Appenzeller, Z. Chen, Z.-G. Chen, H.-M. Cheng, and P. Avouris, "High-performance dual-gate carbon nanotube fets with 40-nm gate length," *IEEE Electr. Device L.*, vol. 26, no. 11, pp. 823–825, Nov. 2005.

- [12] R. Weitz, U. Zschieschang, F. Effenberger, H. Klauk, M. Burghard, and K. Kern, "High-performance carbon nanotube field effect transistors with a thin gate dielectric based on a self-assembled monolayer," *Nano Lett.*, vol. 7, no. 1, pp. 22–27, 2007.

- [13] A. Javey, J. Guo, Q. Wang, M. Lundstrom, and H. Dai, "Ballistic carbon nanotube field-effect transistors," *Nature*, vol. 424, no. 6949, pp. 654–657, 2003

- [14] M. Dresselhaus, G. Dresselhaus, and A. Jorio, "Unusual properties and structure of carbon nanotubes," *Ann. Rev. Mater. Res.*, vol. 34, no. 1, pp. 247–278, 2004.

- [15] G. Dukovic, F. Wang, D. Song, M. Sfeir, T. Heinz, and L. Brus, "Structural dependence of excitonic optical transitions and band-gap energies in carbon nanotubes," *Nano Lett.*, vol. 5, no. 11, pp. 2314–2318, 2005.

- [16] Y. Li, W. Kim, Y. Zhang, M. Rolandi, D. Wang, and H. Dai, "Growth of single-walled carbon nanotubes from discrete catalytic nanoparticles of various sizes," *J. Phys. Chem. B*, vol. 105, no. 46, pp. 11424–11431, 2001.

- [17] A. Kukovecz, C. Kramberger, V. Georgakilas, M. Prato, and H. Kuzmany, "A detailed raman study on thin single-wall carbon nanotubes prepared by the HiPCO process," *Eur. Phys. J. B*, vol. 28, pp. 223–230, 2002.

- [18] G. Lolli, L. Zhang, L. Balzano, N. Sakulchaicharoen, Y. Tan, and D. Resasco, "Tailoring (n,m) structure of single-walled carbon nanotubes by modifying reaction conditions and the nature of the support of CoMo catalysts," *J. Phys. Chem. B*, vol. 110, no. 5, pp. 2108–2115, 2006.

- [19] H. Kataura, Y. Kumazawa, Y. Maniwa, Y. Ohtsuka, R. Sen, S. Suzuki, and Y. Achiba, "Diameter control of single-walled carbon nanotubes," *Carbon*, vol. 38, no. 11–12, pp. 1691–1697, 2000.

- [20] S. Hofmann, R. Sharma, C. Ducati, G. Du, C. Mattevi, C. Cepek, M. Cantoro, S. Pisana, A. Parvez, F. Cervantes Sodi, A. Ferrari, R. Dunin Borkowski, S. Lizzit, L. Petaccia, A. Goldoni, and J. Robertson, "In situ observations of catalyst dynamics during surface-bound carbon nanotube nucleation," *Nano Lett.*, vol. 7, no. 3, pp. 602–608, 2007.

- [21] V. Derycke, R. Martel, J. Appenzeller, and P. Avouris, "Controlling doping and carrier injection in carbon nanotube transistors," *Appl. Phys. Lett.*, vol. 80, no. 15, pp. 2773–2775, 2002.

- [22] S. Suzuki, C. Bower, Y. Watanabe, and O. Zhou, "Work functions and valence band states of pristine and Cs-intercalated single-walled carbon nanotube bundles," *Appl. Phys. Lett.*, vol. 76, no. 26, pp. 4007–4009, 2000.

- [23] Y. Nosho, Y. Ohno, S. Kishimoto, and T. Mizutani, "Relation between conduction property and work function of contact metal in carbon nanotube field-effect transistors," *Nanotechnology*, vol. 17, no. 14, pp. 3412–3415, 2006

- [24] Y.-F. Chen and M. Fuhrer, "Tuning from thermionic emission to ohmic tunnel contacts via doping in Schottky-barrier nanotube transistors," *Nano Lett.*, vol. 6, no. 9, pp. 2158–2162, 2006.

- [25] R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. K. Chan, J. Tersoff, and P. Avouris, "Ambipolar electrical transport in semiconducting singlewall carbon nanotubes," *Phys. Rev. Lett.*, vol. 87, no. 25, pp. 256805-1– 256805-4, 2001.

- [26] T. Durkop, S. Getty, E. Cobas, and M. Fuhrer, "Extraordinary mobility in semiconducting carbon nanotubes," *Nano Lett.*, vol. 4, no. 1, pp. 35–39, 2004.

- [27] S. Auvray, J. Borghetti, M. F. Goffman, A. Filoramo, V. Derycke, J. P. Bourgoin, and O. Jost, "Carbon nanotube transistor optimization by chemical control of the nanotube-metal interface," *Appl. Phys. Lett.*, vol. 84, no. 25, pp. 5106–5108, 2004.

- [28] S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, and P. Avouris, "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes," *Appl. Phys. Lett.*, vol. 80, no. 20, pp. 3817–3819, 2002.

- [29] J. Chen, C. Klinke, A. Afzali, and P. Avouris, "Self-aligned carbon nanotube transistors with charge transfer doping," *Appl. Phys. Lett.*, vol. 86, no. 12, pp. 123108–123111, 2005.

- [30] S. Li, Z. Yu, C. Rutherglen, and P. Burke, "Electrical properties of 0.4 cm long single-walled carbon nanotubes," *Nano Lett.*, vol. 4, no. 10, pp. 2003–2007, 2004.

- [31] R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris, "Single- and multi-wall carbon nanotube field-effect transistors," *Appl. Phys. Lett.*, vol. 73, no. 17, pp. 2447–2449, 1998.

- [32] R. Seidel, A. Graham, J. Kretz, B. Rajasekharan, G. Duesberg, M. Liebau, E. Unger, F. Kreupl, and W. Hoenlein, "Sub-20 nm short channel carbon nanotube transistors," *Nano Lett.*, vol. 5, no. 1, pp. 147–150, 2005.

Simone Pisana (S'99) received the B.A.Sc. degree in engineering science and M.A.Sc. degree in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 2002 and 2004, respectively. He is currently working toward the Ph.D. degree from the Department of Engineering, University of Cambridge, Cambridge, U.K.

His current research interests include growth, characterization, and devices consisting of carbon nanotubes and graphene.

Can Zhang received the B.Eng. degree in materials science and engineering from the University of Leeds, Leeds, U.K., in 2005. He is currently working toward the Ph.D. degree from the Department of Engineering, University of Cambridge, Cambridge, U.K.

His current research interests include carbon nanotubes and their applications in transistors and interconnects.

Caterina Ducati received the Laurea degree in physics from the Universita Statale di Milano, Milano, Italy, in 1999, and the Ph.D. degree in engineering from the University of Cambridge, Cambridge, U.K., in 2003, with specialization in carbon nanotubes and nanostructures for field emission and electrochemistry applications.

She is currently with the Department of Materials Science and Metallurgy, University of Cambridge, as a Postdoctoral Research Associate, where she has been engaged in research on the characterization of

nanocatalysts using electron microscopy techniques. During 2004, she was a Royal Society Dorothy Hodgkin Fellow. During 2007, she was a Royal Society University Research Fellow. Her current research interests include high-resolution electron microscopy analysis of carbon nanotubes and semiconducting nanowires.

**Stephan Hofmann** received the Diplom degree in physics from the Technical University of Munich, Munich, Germany, in 2000, and the Ph.D. degree from the University of Cambridge, Cambridge, U.K., in 2004.

Since 2004, he has been a Research Fellow at Peterhouse, Cambridge, and in 2006, was elected a Royal Society Dorothy Hodgkin Fellow. His current research interests include the catalyst interface dynamics during nanotube/wire growth and related (nano)contact formation.

**John Robertson** (M'07) received the Ph.D. degree in physics from the University of Cambridge, Cambridge, U.K.

He worked in the power generation industry in the United Kingdom for nearly 20 years. He is currently a Professor of Electronics at the Department of Engineering, University of Cambridge. His research interests are electronic materials, including carbon nanotubes, diamond-like carbon, amorphous silicon and large area electronics, silicon dioxide, high dielectric constant gate oxides and metal gate materi-

als. He has authored or coauthored more than 450 papers and he is an Institute for Scientific Information (ISI) highly cited researcher.

Prof. Robertson is the recipient of a Humboldt Research Award from Germany.