# **PAPER • OPEN ACCESS**

# Atomic layer deposited oxide films as protective interface layers for integrated graphene transfer

To cite this article: A Cabrero-Vilatela et al 2017 Nanotechnology 28 485201

View the article online for updates and enhancements.

# Related content

- Encapsulation of graphene transistors and vertical device integration by interface engineering with atomic layer deposited oxide

- Jack A Alexander-Webber, Abhay A Sagade, Adrianus I Aria et al.

- A reliable and controllable graphene doping method compatible with current CMOS technology and the demonstration of its device applications Seonyeong Kim, Somyeong Shin, Taekwang Kim et al.

- Polymer-free graphene transfer for enhanced reliability of graphene fieldeffect transistors

Hamin Park, Ick-Joon Park, Dae Yool Jung et al.

# Atomic layer deposited oxide films as protective interface layers for integrated graphene transfer

A Cabrero-Vilatela<sup>1</sup>, J A Alexander-Webber<sup>1,4</sup>, A A Sagade<sup>1,5</sup>, A I Aria<sup>1,2</sup>, P Braeuninger-Weimer<sup>1</sup>, M-B Martin<sup>1</sup>, R S Weatherup<sup>1,3</sup> and S Hofmann<sup>1,4</sup>

E-mail: jaa59@cam.ac.uk and sh315@cam.ac.uk

Received 24 August 2017, revised 12 October 2017 Accepted for publication 17 October 2017 Published 6 November 2017

#### Abstract

The transfer of chemical vapour deposited graphene from its parent growth catalyst has become a bottleneck for many of its emerging applications. The sacrificial polymer layers that are typically deposited onto graphene for mechanical support during transfer are challenging to remove completely and hence leave graphene and subsequent device interfaces contaminated. Here, we report on the use of atomic layer deposited (ALD) oxide films as protective interface and support layers during graphene transfer. The method avoids any direct contact of the graphene with polymers and through the use of thicker ALD layers ( $\geqslant 100 \, \text{nm}$ ), polymers can be eliminated from the transfer-process altogether. The ALD film can be kept as a functional device layer, facilitating integrated device manufacturing. We demonstrate back-gated field effect devices based on single-layer graphene transferred with a protective  $\text{Al}_2\text{O}_3$  film onto  $\text{SiO}_2$  that show significantly reduced charge trap and residual carrier densities. We critically discuss the advantages and challenges of processing graphene/ALD bilayer structures.

Supplementary material for this article is available online

Keywords: graphene, transfer, chemical vapour deposition, atomic layer deposition

(Some figures may appear in colour only in the online journal)

# Introduction

1

Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

The development of scalable integrated manufacturing pathways for graphene and related 2D materials is crucial to all their emerging applications and industrial development. Significant progress has been made in 2D crystal growth [1–3], and monolayer graphene crystals beyond the cm-scale [4] and continuous films over areas just limited by the growth reactor geometry [5–7] are now routinely achieved by chemical vapour deposition (CVD). The graphene CVD process utilises a catalytic substrate to achieve high crystallinity [2, 8–10] and for the

<sup>&</sup>lt;sup>1</sup> Department of Engineering, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 0FA, United Kingdom

<sup>&</sup>lt;sup>2</sup> Surface Engineering and Nanotechnology Institute, School of Aerospace, Transport and Manufacturing, Cranfield University, College Road, Cranfield, MK43 0AL, United Kingdom

<sup>&</sup>lt;sup>3</sup> Materials Sciences Division, Lawrence Berkeley National Laboratory, 1 Cyclotron Road, Berkeley, CA 94720, United States of America

Authors to whom any correspondence should be addressed.

Present address: SRM Research Institute and Department of Physics & Nanotechnology, SRM University, Kattankulathur, 603 203, Tamil Nadu, India.

majority of emerging applications the graphene has to be released from this parent growth substrate and transferred into the device stack. To achieve such graphene transfer cleanly and without damage, in order that the unique properties of graphene are preserved, has become a critical challenge [11–15]. This challenge is particularly highlighted by the many proposed (opto-)electronic graphene devices, starting with simple gated graphene field effect device structures, for which the graphene performance is found to be highly sensitive to the presence of any contaminants [16-19]. Most polymer [20-24] and metal [25, 26] layers used as temporary mechanical supports during graphene transfer have been shown to leave residues on graphene after removal, degrading its electronic properties [12, 27, 28]. Other common contaminants include lithographic resists, organic solvents, etching products and ambient air [29], all of which can for instance unintentionally dope the graphene (generally p-type [17]) and cause hysteresis in field effect devices [30]. Hence, ideally the graphene should be protected from any such contamination during transfer and processing as well as during device operation. A number of approaches have been proposed in recent literature to address these challenges. The cleanest graphene device interfaces have been achieved via van-der-Waals heterostructures, particularly graphene sandwiched between h-BN crystals [31-33], using dry transfer techniques which, however, have limited scalability and rely on the availability and quality of other 2D materials. The use of different polymer layers to support graphene transfer and act as part of optoelectronic devices has also been reported but this is limited to certain applications [34–36]. Thin ( $\sim$ 1 nm) metal oxide layers such as Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, NiO and Cr<sub>2</sub>O<sub>3</sub> directly evaporated onto graphene prior to transfer have been used as protection from direct polymer exposure [37]. Whereas graphene encapsulation with atomic layer deposited (ALD) alumina at the post-transfer stage has enabled reproducible device behaviour with negligible gate hysteresis and low doping levels [38–40]. Due to its scalability and atomic layer growth control, ALD is particularly suited to be used in conjunction with CVD graphene, and initial progress has been made in exploring the ALD parameter space to achieve conformal nucleation of ultrathin oxides on graphene and to improve rational 2D/non-2D material integration [41–44].

Here, we explore the concept of using ALD oxide films for CVD graphene device fabrication in a combined, integrated fashion where the same ALD layer can serve as graphene protection, support, encapsulation and functional device layer. The method avoids any direct contact of the graphene with polymers and through the use of thicker ALD layers (≥100 nm), polymers can be eliminated from the transfer-process altogether. We focus on alumina (Al<sub>2</sub>O<sub>3</sub>), hafnia (HfO<sub>2</sub>) and titania (TiO<sub>2</sub>) ALD layers based on their extensive use in electronic devices as, for instance, high- $\kappa$ dielectric [38, 42], tunnel barrier [42, 45] or permeation barrier [46, 47]. We demonstrate back-gated field effect devices based on single-layer graphene transferred with a protective Al<sub>2</sub>O<sub>3</sub> film onto SiO<sub>2</sub> that show significantly reduced charge trap and residual carrier densities. We critically discuss the advantages and challenges of such integrated approaches, and in particular how this relates to the processing of graphene/ALD bilayer structures.

## Methods

Graphene is synthesized by CVD in a commercially available Aixtron BM Pro (4 inch) machine using polycrystalline Cu foils (Alfa Aesar, 25  $\mu$ m thick, 99.8% purity). Catalysts are annealed for 30 min at 50 mbar in a mixture of H<sub>2</sub>/Ar at 1065 °C. CH<sub>4</sub> diluted to 0.1% in Ar is then introduced to the chamber for 45 min promoting growth under a CH<sub>4</sub>/H<sub>2</sub>/Ar atmosphere and finally cooled down to room temperature in Ar [48].

A Cambridge Nanotech Savannah System (S100 G1) was employed for the deposition of the oxide layers. H<sub>2</sub>O was used as oxidant during ALD and the precursors for titania, alumina and hafnia were tetrakis(dimethylamido)titanium (TDMAT, purity >99% Sigma Aldrich 669008), trimethylaluminum (TMA, purity >98%, Strem Chemicals 93-1360) and tetrakis (dimethylamido)hafnium (TDMAHf, purity >99% Sigma Aldrich 455199) respectively. Precursors are volatised at temperatures of 40 °C for H<sub>2</sub>O and TMA and 75 °C for TDMAT and TDMAHf. All samples are loaded and unloaded while the chamber is at deposition temperature (200 °C for hafnia and alumina and 120 °C for titania). Before the ALD deposition, the chamber is pumped to reach a base pressure of  $\sim 6 \times 10^{-1}$  mbar and purged with 20 sccm N<sub>2</sub> for 10 min. Oxidant and precursors are alternately introduced into the chamber in a 20 sccm flow of N2 carrier gas, which is the same flow employed during the purging time. Recipes were optimised to provide a continuous film. Details of the ALD growth can be found in the supporting information, available online at stacks.iop.org/NANO/28/485201/mmedia.

Polymer-supported graphene transfer is performed by depositing poly methyl methacrylate (PMMA) onto the graphene/metal-catalyst sample. The catalyst is removed by etching in a  $0.5\,\mathrm{M}$  FeCl $_3$  aqueous solution. The graphene/polymer film is rinsed in DI water and then transferred to  $\mathrm{SiO}_2(300\,\mathrm{nm})/\mathrm{Si}$  substrate. The polymer support is subsequently removed by immersion in acetone followed by rinsing in IPA and drying under a  $\mathrm{N}_2$  flow.

Exposure of graphene/oxide to ozone was carried out in the Cambridge Nanotech Savannah System (S100 G1). A series of ozone pulses were performed over one minute each with a dose of  $\sim$ 40 mbar s and  $N_2$  purge of 1 s between pulses.

Optical microscopy and Raman spectroscopy (Renishaw Raman InVia microscope, 632 nm wavelength with 1 mW delivered to the sample, 50x objective) are performed after graphene is transferred to SiO<sub>2</sub>(300 nm)/Si substrates.

# Results

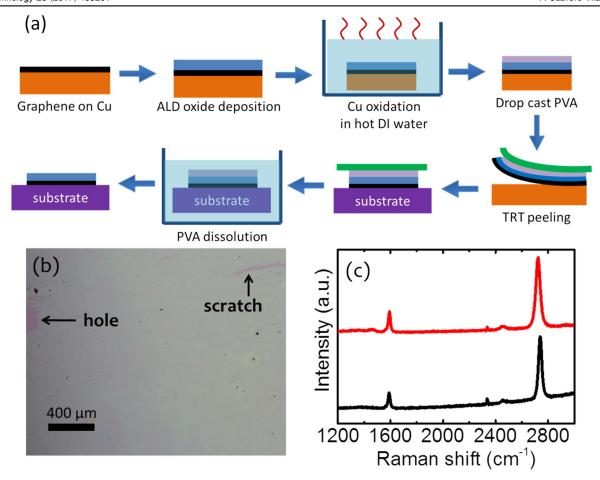

Figure 1(a) schematically outlines our etching-free transfer process using ALD alumina as support layer. The first step is the ALD of alumina directly onto CVD graphene-covered Cu catalyst foil (more details in supporting information) under continuous-flow mode without a seed layer [41]. As

**Figure 1.** (a) Schematic representation of the transfer process with oxide buffer layer between graphene and polymer. (b) Optical micrograph of graphene transferred to SiO<sub>2</sub>(300 nm)/Si using the process shown in (a). (c) Raman spectra of as-grown graphene on Cu foil – black line– and of graphene transferred to SiO<sub>2</sub>(300 nm)/Si using the process shown in (a) –red line–.

confirmed by spectroscopic ellipsometry, a 40 nm ALD oxide thickness was used here, noting that the oxide thickness can be adapted to a chosen application, for example to achieve a certain gate oxide thickness in top-gated transistors. The sample is then immersed in DI water at  $\sim$ 50 °C for  $\sim$ 12 h to oxidize the Cu foil. The creation of Cu oxide decouples the graphene from the catalyst [49-51] making it easier to peel from the Cu foil. A poly(vinyl) alcohol (PVA) solution (2 g in 20 ml DI water) is drop-cast on top of the alumina layer and heated to 70 °C for 10 min [52] to provide additional mechanical support for the graphene/alumina film. The sample is removed from the hot plate and a thermal release tape (TRT) (Nitto Denko) is placed on top of it. The Cu foil is then peeled off and the TRT-PVA-alumina-graphene layer stack is transferred onto a SiO<sub>2</sub>(300 nm)/Si support for the fabrication of field effect transistors (FETs). We acknowledge that the formation of wrinkles, cracks and holes can occur as a result of this process, as highlighted in figure 1(b). After the transfer, the substrate is heated to 120 °C to ensure the release of the TRT. The sample is then immersed in warm DI water (50 °C) for at least 1 h to dissolve the PVA and finally dried with N<sub>2</sub>. We highlight that although Cu foils are used here, the use of oxides to support graphene transfer is a method applicable to graphene grown on other CVD metal catalysts where other treatments can be used to weaken the graphene—catalyst interaction.

We use optical microscopy and Raman spectroscopy for the initial characterisation of as-transferred graphene. Figure 1(b) shows an optical image of the transferred graphene/alumina bilayer, where the contrast with the SiO<sub>2</sub>(300 nm)/Si support is highlighted by a hole and a scratch in the film. Figure 1(c) compares the Raman spectrum of as-grown CVD graphene on Cu foil (black line) with graphene transferred onto SiO<sub>2</sub>(300 nm)/Si with 40 nm of alumina (red line) using the process described in figure 1(a). Both samples show the characteristic features of single layer graphene (2D FWHM  $<40 \,\mathrm{cm}^{-1}$  and  $I_{\mathrm{2D}}/I_{\mathrm{G}} > 2$ ) whilst the negligible D peak confirms high graphitic quality and negligible defects and disorders introduced by this transfer process. As-grown graphene on Cu shows a 2D peak fitted with a single Lorentzian with FWHM = 36.9,  $I_{2D}/I_{G}$  = 3.4 and the G and 2D peak positions at 1590 cm<sup>-1</sup> and 2740 cm<sup>-1</sup>, respectively. Raman spectra collected on graphene after transfer shows a 2D peak fitted with a single Lorentzian with FWHM = 38.5,  $I_{2D}/I_G$  = 3.1 and the G and 2D peak positions at  $1593 \,\mathrm{cm}^{-1}$  and  $2723 \,\mathrm{cm}^{-1}$ , respectively.

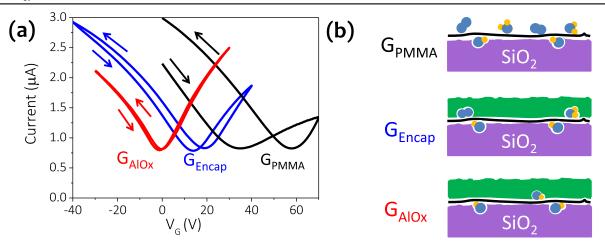

**Figure 2.** (a) Transfer characteristics of back-gated two terminal transistors fabricated with three different processing approaches, as described in the main text. Source–drain bias was  $V_{\rm SD}=10~{\rm mV}$ . (b) Schematic representation of graphene/metal-oxide/SiO<sub>2</sub> interface of various devices measured in (a).

One of the most common graphene device architectures, that serves as a building block for a number of graphene applications, is the FET. There are a number of key metrics which may be used to define FET device performance. Whilst particular effort has been focussed on improving the fieldeffect mobility [39, 53, 54], real-world applications have stringent requirements on stable and consistent operation. As such, additional factors including gate-induced hysteresis and unintentional doping are crucial parameters to be minimised for graphene applications. Back-gated (300 nm SiO<sub>2</sub> on doped-Si) graphene FET devices were fabricated using photolithography (see Methods and supporting information) to further characterise the graphene. All electrical measurements were carried out in ambient conditions at room temperature. We use three different processing approaches to fabricate graphene-based FETs (as described further in the supporting information): (1) transfer with PMMA support layer  $[G_{PMMA}]$ , (2) transfer with PMMA followed by the posttransfer deposition of 40 nm ALD alumina [ $G_{\text{Encap}}$ ] and (3) depositing 40 nm alumina as protective layer prior to transfer using the method outlined in figure 1(a) [ $G_{AlO_x}$ ]. For the latter approach the alumina was selectively etched in diluted phosphoric acid to allow contact metallisation whilst leaving the graphene channel protected, as described in the supporting information.

By measuring the Dirac point  $V_{\rm D}$ , i.e. the gate voltage at which minimum current is observed, and the change in  $V_{\rm D}$  between the up sweep (negative to positive) and the down sweep (positive to negative)  $\Delta V_{\rm D}$ , we can extract the interface charge trap density  $\Delta n = C_{\rm g} \Delta V_{\rm D}/e$ , as well as the residual carrier density (calculated for the up sweep)  $n_{\rm res} = C_{\rm g} V_{\rm D}/e$ , where the gate capacitance  $C_{\rm g} = 11.6~{\rm nFcm^{-2}}$ , and e is the electronic charge. Figure 2(a) shows the field-effect transport characteristics of devices fabricated via the three different graphene processing approaches. The  $G_{\rm PMMA}$  FET shows high p-type doping  $(n_{\rm res} > 2 \times 10^{12}~{\rm cm^{-2}})$  and a large hysteresis between the up and the down sweeps  $(\Delta n > 1.6 \times 10^{12}~{\rm cm^{-2}})$  which is typical for unencapsulated graphene on SiO<sub>2</sub> transferred with PMMA. A significant but incomplete reduction in

**Table 1.** Comparison of the charge trap density  $\Delta n$ , and residual carrier density  $n_{\text{res}}$  (determined from the up sweep) extracted from the plots in figure 2 and compared to values in the literature.

| Graphene process                                                             | $\Delta n \times 10^{10}$ $(\text{cm}^{-2})$ | $n_{\rm res} \times 10^{10}$ (cm <sup>-2</sup> ) |

|------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|

| $G_{ m PMMA}$                                                                | 165                                          | 254                                              |

| $G_{ m Encap}$                                                               | 37                                           | 102                                              |

| $G_{ m AlO_x}$                                                               | 6                                            | 7                                                |

| 30 nm ALD Al <sub>2</sub> O <sub>3</sub> [55]                                | 86                                           | Not given                                        |

| 90 nm ALD Al <sub>2</sub> O <sub>3</sub> —Oxidised Al seed layer [38]        | 0–17                                         | 11.5                                             |

| 90 nm ALD Al <sub>2</sub> O <sub>3</sub> —H <sub>2</sub> O pretreatment [39] | 6                                            | 14.5                                             |

hysteresis and doping can be obtained for  $G_{\rm Encap}$ , which is consistent with previous reports after the direct deposition of ALD alumina on polymer transferred graphene [55]. Further improvements can be obtained using thicker encapsulating films as well as optimised seed layers [38]. The long term encapsulation of graphene transistors has also been demonstrated using *in situ* gaseous pretreatments where conformal growth of oxide passivates charge traps on the graphene surface [39]. However, these methods use graphene after transfer with PMMA and thus, are prone to the degradation it involves. Ultimately during the initial exposure to PMMA during transfer some adsorbates will remain trapped between the graphene and alumina layer after encapsulation causing a finite level of doping and hysteresis, as schematically shown in figure 2(b).

The  $I_{\rm D}-V_{\rm G}$  behaviour of  $G_{\rm AlO_x}$  (figure 2(a)) shows negligible doping ( $n_{\rm res}<1\times10^{11}\,{\rm cm}^{-2}$ ) and very low hysteresis ( $\Delta n<1\times10^{11}\,{\rm cm}^{-2}$ ) compared to  $G_{\rm Encap}$ . Given that the same ALD growth conditions were used for each process, the clear improvement between  $G_{\rm Encap}$  and  $G_{\rm AlO_x}$  can thus be predominantly attributed to the significant reduction in the number of processing-induced adsorbents at the interface between graphene and alumina, as schematically shown in figure 2(b). Table 1 compares the FET device metrics for

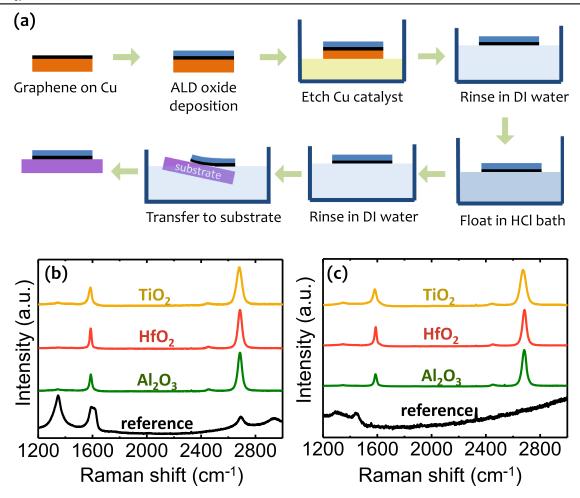

**Figure 3.** (a) Schematic representation of the second oxide transfer process where polymer is completely avoided. Comparison of Raman spectra of graphene transferred with metal oxide layers and  $G_{PMMA}$  as reference after exposing to harsh gas environments: (b) ozone treatment for 1 min at 200 °C, which is comprised of a series of ozone pulses each with a dose of  $\sim$ 40 mbar s and  $N_2$  purge between pulses of 1 s in the same system used for ALD and (c) oxygen plasma for 1 min at 100 W and 150 mbar.

the three different processes, which for  $G_{AIO_x}$  devices are comparable with some of the lowest hysteresis values for graphene FETs in the literature [38, 39]. This highlights the benefits of the proof-of-concept oxide transfer technique demonstrated here, that avoids any direct contact of the graphene with polymers or etchants.

The use of polymers during the transfer process can be completely avoided by depositing a thicker layer of ALD metal oxide. Figure 3(a) shows the steps followed for this transfer method. 100 nm of either alumina, hafnia or titania are directly deposited onto graphene on Cu foil under continuous-flow mode without using a seed layer [41]. The thickness was determined to give enough support to the graphene during the transfer process which simultaneously provides more stability to graphene devices due to its encapsulation [38]. Cu foil is then etched using a 0.5 M FeCl<sub>3</sub> aqueous solution ( $\sim$ 12 h) for a sample size of 1  $\times$  1 cm<sup>2</sup> and transferred to DI water. Samples are then floated in HCl 37% for 15 min to remove any residual Fe ions left from the etchant [56]. A second DI water bath is used to rinse the samples and they are finally removed from the water onto a SiO<sub>2</sub>(300 nm)/Si substrate.

Additional tests were carried out to confirm the robustness of the film transferred with the metal oxides. Three samples of SLG were transferred each with a 100 nm thick layer titania, hafnia and alumina, respectively, following the process outlined in figure 3(a). Samples of graphene transferred with each of the metal oxides were heated to 200 °C and exposed to ozone for 1 min (see methods for more details). Furthermore, different samples of graphene transferred with the three metal oxides were exposed to oxygen plasma (1 min, 100 W, 150 mbar) at room temperature. Reference samples of SLG transferred with conventional processes using PMMA and not protected with a metal oxide layer were also exposed to ozone and oxygen plasma at the same time.

Raman spectra taken from the top of the samples after oxygen plasma and ozone treatments are shown in figures 3(b) and (c). The annealing of unprotected graphene under an oxidizing atmosphere such as ozone leads to degradation as shown for the unprotected reference sample in figure 3(b) (black line). Similarly, the conditions used for the oxygen plasma are expected to completely remove unprotected graphene, since a shorter (8 s) and lower power (50 W)

oxygen plasma treatment performed at the same pressure on a sample without any metal oxide layer leads to the complete absence of a 2D peak in the Raman spectra, as observed in figure 3(c) (black line). The samples transferred with the oxide support layers show no significant increase in the measured D-peak of the Raman spectra after the ozone and oxygen plasma treatments. This confirms the oxide support layer effectively protects the SLG from harsh oxidising environments maintaining the quality of the graphene.

## **Discussion**

While ALD of metal oxides has been widely used for graphene FETs, here we demonstrate a more integrated approach to device fabrication, where the same ALD layer can serve as graphene protection, support, encapsulation and functional device layer. Our data showed that a 40 nm ALD alumina layer directly deposited on the graphene/catalyst after the growth enables a significant reduction in the number of processing-induced adsorbents during FET fabrication and hence significantly reduced charge trap and residual carrier densities. Our method aides integrated device manufacturing, effectively eliminating an additional step. While ALD films offer graphene protection, selective etching of the oxide is required to contact the graphene for typical device structures. The selective etching of oxide films has been well studied and multiple methods have been reported including wet [57, 58] (e.g. KOH, HF, piranha) and dry [59-62] (e.g. RIE, ICP, DRIE) processes. However, we found that etching of the metal-oxide layer here was not straight forward which may relate in part to the growth mechanisms of ALD oxides on graphene [41]. Extensive process calibration was required to avoid leaving oxide residues or damaging the graphene. Although we note that complete etching of the graphene might be beneficial in the contact area to lower contact resistance by producing edge contacts (side contact instead of top contact) [63–65].

Our method here relies on the transfer and processing of graphene/ALD bilayer structures. ALD oxide growth is conformal and thus, is prone to 'freeze in' graphene wrinkles on the catalyst surface (see atomic force microscopy in supporting information) which can be detrimental to the transport properties. The transfer process can also introduce strain in the graphene and damage the oxide and graphene films. The transfer process involves handling and bending of the oxide/ graphene film which can induce cracks that may lead to significant reduction of film quality. The thinner the oxide layer the more flexible it is, and according to literature 40 nm films of ALD deposited alumina start showing cracks at a bending radius of 14 mm [66]. To partly address these challenges, our method can be modified into a two-stage process where following the initial transfer with a thin ALD layer an additional layer of oxide is deposited.

We have so far considered the ALD oxide/graphene interface, however, the substrate interface is equally important for device performance. We focus here on SiO<sub>2</sub> as the most widely used support, yet it is well known that the measured

graphene mobility is limited by its interaction with this substrate [67, 68]. This can be addressed via alternative support (such as h-BN) [67], or partly by plasma treatments and reoxidation of the  $SiO_2$  substrate [69]. Furthermore, we have shown that during oxide ALD,  $H_2O/O_2$  redox couples and the presence of silanol groups at the graphene— $SiO_2$  interface can cause doping and hysteretic behaviour [30, 38, 70]. So apart from just avoiding substrate contamination, it is also important to ensure the integrity of the relevant device interfaces during the entire process flow.

Herein, we focus on FET model devices, but this integrated approach may be interesting for a wide range of graphene applications where scalability and reliable device performance are critical challenges. For dye-sensitized solar cells [71–73], for instance, using ALD titania as the support layer would provide a clean interface between the graphene and the titania whilst the titania can also serve as a compact layer to reduce charge recombination losses [74]. It is conceivable that dopant materials could be incorporated at the graphene-oxide interface to strongly dope the graphene for applications requiring low sheet resistance such as organic light emitting diodes [75]. The oxide support may also be exploited as a hard mask [76] in devices avoiding the use of polymers and other organic solvents that can leave undesirable carbon residues on the graphene surface.

# **Conclusions**

We have demonstrated the concept of using ALD oxide films not only for graphene interfacing and post-growth encapsulation but also as a protective and supporting layer for CVD graphene transfer and integrated FET fabrication. Back-gated graphene FET devices transferred with ALD alumina show significantly reduced charge trap and residual carrier densities. Our method avoids any direct contact of the graphene with polymers and through the use of thicker ALD layers (≥100 nm), polymers can be eliminated from the transfer-process altogether. The ALD film can be kept as a functional device layer, facilitating integrated device manufacture. Many of the challenges for 2D materials are essentially linked to interfacing with non-2D materials and we think the combination of CVD and ALD thereby offers many opportunities that underline the wider relevance of our data here.

# **Acknowledgments**

We acknowledge funding from EPSRC (Grant No. EP/K016636/1, GRAPHTED) and ERC (Grant No. 279342, InsituNANO). ACV acknowledges the Conacyt Cambridge Scholarship and Roberto Rocca Fellowship. JAA-W acknowledges the support of his Research Fellowships from the Royal Commission for the Exhibition of 1851 and Churchill College, Cambridge. RSW acknowledges a Research Fellowship from St. John's College, Cambridge and a Marie Skłodowska-Curie Individual Fellowship (Global) under grant ARTIST (no. 656870)

from the European Union's Horizon 2020 research and innovation programme.

#### **ORCID iDs**

J A Alexander-Webber https://orcid.org/0000-0002-9374-7423

A A Sagade https://orcid.org/0000-0002-3299-7103

A I Aria https://orcid.org/0000-0002-6305-3906

S Hofmann https://orcid.org/0000-0001-6375-1459

#### References

- Xu X et al 2016 Ultrafast growth of single-crystal graphene assisted by a continuous oxygen supply Nat. Nanotechnol. 11 930-5

- [2] Hofmann S, Braeuninger-Weimer P and Weatherup R S 2015 CVD-enabled graphene manufacture and technology J. Phys. Chem. Lett. 6 2714–21

- [3] Wu T et al 2016 Fast growth of inch-sized single-crystalline graphene from a controlled single nucleus on Cu–Ni alloys Nat. Mater. 15 43–7

- [4] Xu X et al 2017 Ultrafast epitaxial growth of metre-sized singlecrystal graphene on industrial Cu foil Sci. Bull. 62 1074–80

- [5] Kobayashi T et al 2013 Production of a 100 m-long highquality graphene transparent conductive film by roll-to-roll chemical vapor deposition and transfer process Appl. Phys. Lett. 102 023112

- [6] Polsen E S, McNerny D Q, Viswanath B, Pattinson S W and John Hart A 2015 High-speed roll-to-roll manufacturing of graphene using a concentric tube CVD reactor Sci. Rep. 5 10257

- [7] Ryu J et al 2014 Fast synthesis of high-performance graphene films by hydrogen-free rapid thermal chemical vapor deposition ACS Nano 8 950–6

- [8] Oshima C and Nagashima A 1997 Ultra-thin epitaxial films of graphite and hexagonal boron nitride on solid surfaces J. Phys. Condens. Matter 9 1–20

- [9] Dahal A and Batzill M 2014 Graphene–nickel interfaces: a review *Nanoscale* 6 2548–62

- [10] Cabrero-Vilatela A, Weatherup R S, Braeuninger-Weimer P, Caneva S and Hofmann S 2015 Towards a general growth model for graphene CVD on transition metal catalysts *Nanoscale* 8 2149

- [11] Chen Y, Gong X L and Gai J G 2016 Progress and challenges in transfer of large-area graphene films Adv. Sci. 3 1500343

- [12] Cheng Z, Zhou Q, Wang C, Li Q and Fang Y 2011 Toward intrinsic graphene surfaces: a systematic study on thermal annealing and wet-chemical treatment of SiO<sub>2</sub>-supported graphene devices *Nano Lett.* 11 767–71

- [13] Choi J-Y 2013 Graphene transfer: a stamp for all substrates Nat. Nanotechnol. 8 311–2

- [14] Liang X et al 2011 Toward clean and crackless transfer of graphene ACS Nano 5 9144–53

- [15] Lin Y-C, Lu C-C, Yeh C-H, Jin C, Suenaga K and Chiu P-W 2012 Graphene annealing: how clean can it be? *Nano Lett.* 12 414-9

- [16] Ryu S, Liu L, Berciaud S, Yu Y-J, Liu H, Kim P, Flynn G W and Brus L E 2010 Atmospheric oxygen binding and hole doping in deformed graphene on a SiO<sub>2</sub> substrate *Nano Lett.* 10 4944–51

- [17] Levesque P L, Sabri S S, Aguirre C M, Guillemette J, Siaj M, Desjardins P, Szkopek T and Martel R 2011 Probing charge transfer at surfaces using graphene transistors *Nano Lett.* 11 132–7

- [18] Schedin F, Geim A K, Morozov S V, Hill E W, Blake P, Katsnelson M I and Novoselov K S 2007 Detection of individual gas molecules adsorbed on graphene *Nat. Mater.* 6 652–5

- [19] Chen J-H, Jang C, Adam S, Fuhrer M S, Williams E D and Ishigami M 2008 Charged-impurity scattering in graphene Nat. Phys. 4 377–81

- [20] Gao L, Ni G-X, Liu Y, Liu B, Castro Neto A H and Loh K P 2014 Face-to-face transfer of wafer-scale graphene films Nature 505 190–4

- [21] Bae S *et al* 2010 Roll-to-roll production of 30-inch graphene films for transparent electrodes *Nat. Nanotechnol.* **5** 574

- [22] Kim S J et al 2015 Ultraclean patterned transfer of single-layer graphene by recyclable pressure sensitive adhesive films Nano Lett. 15 3236–40

- [23] Kim H H, Kang B, Suk J, Li N, Kim S, Ruoff R S, Lee W H and Cho K 2015 Clean transfer of wafer-scale graphene via liquid phase removal of polycyclic aromatic hydrocarbons clean transfer of wafer-scale graphene via liquid phase removal of polycyclic aromatic hydrocarbons ACS Nano 9 4726–33

- [24] Wood J D et al 2015 Annealing free, clean graphene transfer using alternative polymer scaffolds Nanotechnology 26 055302

- [25] Choi J, Kim H, Park J, Iqbal M W, Iqbal M Z, Eom J and Jung J 2014 Enhanced performance of graphene by using gold film for transfer and masking process *Curr. Appl. Phys.* 14 1045–50

- [26] Lemaitre M G, Donoghue E P, Mccarthy M A, Liu B, Tongay S, Gila B, Kumar P, Singh R K, Appleton B R and Rinzler A G 2012 Improved transfer of graphene for organic, field-effect transistors ACS Nano 6 9095–102

- [27] Kratzer M, Bayer B C, Kidambi P R, Aleksandar M, Gajic R, Cabrero-Vilatela A, Weatherup R S, Hofmann S and Teichert C 2016 Effects of polymethylmethacrylate-transfer residues on the growth of organic semiconductor molecules on chemical vapor deposited graphene Appl. Phys. Lett. 106 103101

- [28] Pirkle A, Chan J, Venugopal A, Hinojos D, Magnuson C W, McDonnell S, Colombo L, Vogel E M, Ruoff R S and Wallace R M 2011 The effect of chemical residues on the physical and electrical properties of chemical vapor deposited graphene transferred to SiO<sub>2</sub> Appl. Phys. Lett. 99 122108

- [29] Aria A I, Kidambi P R, Weatherup R S, Xiao L, Williams J A and Hofmann S 2016 Time evolution of the wettability of supported graphene under ambient air exposure *J. Phys. Chem.* C 120 2215–24

- [30] Wang H, Wu Y, Cong C, Shang J and Yu T 2010 Hysteresis of electronic transport in graphene transistors ACS Nano 4 7221–8

- [31] Pizzocchero F, Gammelgaard L, Jessen B S, Caridad J M, Wang L, Hone J, Bøggild P and Booth T J 2016 The hot pick-up technique for batch assembly of van der Waals heterostructures *Nat. Commun.* 7 11894

- [32] Dean C R *et al* 2010 Boron nitride substrates for high-quality graphene electronics *Nat. Nanotechnol.* **5** 722–6

- [33] Banszerus L, Schmitz M, Engels S, Dauber J, Oellers M, Haupt F, Watanabe K, Taniguchi T, Beschoten B and Stampfer C 2015 Ultrahigh-mobility graphene devices from chemical vapor deposition on reusable copper Sci. Adv. 1 1500222

- [34] Lee W H *et al* 2012 Simultaneous transfer and doping of CVD-grown graphene by fluoropolymer for transparent conductive films on plastic *ACS Nano* **6** 1284–90

- [35] de Castro R K, Araujo J R, Valaski R, Costa L O O, Archanjo B S, Fragneaud B, Cremona M and Achete C A 2015 New transfer method of CVD-grown graphene using a flexible, transparent and conductive polyaniline-rubber thin film for organic electronic applications *Chem. Eng. J.* 273 (Suppl C) 509–18

- [36] Lee B H, Lee J-H, Kahng Y H, Kim N, Kim Y J, Lee J, Lee T and Lee K 2014 Graphene-conducting polymer hybrid transparent electrodes for efficient organic optoelectronic devices Adv. Funct. Mater. 24 1847–56

- [37] Yamaguchi J, Hayashi K, Sato S and Yokoyama N 2013 Passivating chemical vapor deposited graphene with metal oxides for transfer and transistor fabrication processes Appl. Phys. Lett. 102 143505

- [38] Sagade A A, Neumaier D, Schall D, Otto M, Pesquera A, Centeno A, Elorza A Z and Kurz H 2015 Highly air stable passivation of graphene based field effect devices *Nanoscale* 7 3558–64

- [39] Alexander-Webber J A et al 2017 Encapsulation of graphene transistors and vertical device integration by interface engineering with atomic layer deposited oxide 2D Mater. 4 011008

- [40] Kindness S J et al 2017 External amplitude and frequency modulation of a terahertz quantum cascade laser using metamaterial/graphene devices Sci. Rep. 7

- [41] Aria A I, Nakanishi K, Xiao L, Braeuninger-Weimer P, Sagade A A, Alexander-Webber J A and Hofmann S 2016 Parameter space of atomic layer deposition of ultrathin oxides on graphene ACS Appl. Mater. Interfaces 8 30564–75

- [42] Martin M, Dlubak B, Weatherup R S, Yang H, Deranlot C, Anane A, Hofmann S, Robertson J, Bouzehouane K and Al M E T 2014 Sub-nanometer atomic layer deposition for spintronics in magnetic tunnel junctions based on graphene spin-filtering membranes ACS Nano 8 7890–5

- [43] Oh I-K et al 2015 Nucleation and growth of the HfO<sub>2</sub> dielectric layer for graphene-based devices Chem. Mater. 27 5868–77

- [44] Shin W C, Bong J H, Choi S-Y and Cho B J 2013

Functionalized graphene as an ultrathin seed layer for the atomic layer deposition of conformal high-k dielectrics on graphene ACS Appl. Mater. Interfaces 5 11515–9

- [45] Dlubak B *et al* 2012 Highly efficient spin transport in epitaxial graphene on SiC *Nat. Phys.* **8** 557–61

- [46] Langereis E, Creatore M, Heil S B S, Van De Sanden M C M and Kessels W M M 2016 Plasmaassisted atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> moisture permeation barriers on polymers *Appl. Phys. Lett.* 89 081915

- [47] Yun S J, Ko Y-W and Lim J W 2004 Passivation of organic light-emitting diodes with aluminum oxide thin films grown by plasma-enhanced atomic layer deposition *Appl. Phys. Lett.* 85 4896–8

- [48] Braeuninger-Weimer P, Brennan B, Pollard A J and Hofmann S 2016 Understanding and controlling Cucatalyzed graphene nucleation: the role of impurities, roughness, and oxygen scavenging *Chem. Mater.* 28 2005, 15

- [49] Kidambi P R, Bayer B C, Blume R, Wang Z-J, Baehtz C, Weatherup R S, Willinger M-G, Schloegl R and Hofmann S 2013 Observing graphene grow: catalyst–graphene interactions during scalable graphene growth on polycrystalline copper *Nano Lett.* 13 4769–78

- [50] Chandrashekar B N, Deng B, Smitha A S, Chen Y, Tan C, Zhang H, Peng H and Liu Z 2015 Roll-to-roll green transfer of CVD graphene onto plastic for a transparent and flexible triboelectric nanogenerator Adv. Mater. 27 5210–6

- [51] Wang R et al 2016 Catalyst interface engineering for improved 2D film lift-off and transfer ACS Appl. Mater. Interfaces 8 33072.

- [52] Yang S Y, Oh J G, Jung D Y, Choi H, Yu C H, Shin J, Choi C G, Cho B J and Choi S Y 2015 Metal-etching-free direct delamination and transfer of single-layer graphene with a high degree of freedom Small 11 175–81

- [53] Wu Z et al 2015 A fast transfer-free synthesis of high-quality monolayer graphene on insulating substrates by a simple rapid thermal treatment *Nanoscale* 8 2594–600

- [54] Kim S, Nah J, Jo I, Shahrjerdi D, Colombo L, Yao Z, Tutuc E and Banerjee S K 2009 Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric Appl. Phys. Lett. 94 062107

- [55] Lee Y G, Kang C G, Cho C, Kim Y, Hwang H J and Lee B H 2013 Quantitative analysis of hysteretic reactions at the interface of graphene and SiO<sub>2</sub> using the short pulse I–V method *Carbon N. Y.* 60 453–60

- [56] Dai B, Fu L, Zou Z, Wang M, Xu H, Wang S and Liu Z 2011 Rational design of a binary metal alloy for chemical vapour deposition growth of uniform single-layer graphene *Nat. Commun.* 2 522

- [57] Williams K R, Member S, Gupta K, Member S and Wasilik M 2003 Etch rates for micromachining processing: II *IEEE* 12 761–78

- [58] Lowalekar V and Raghavan S 2011 Etching of zirconium oxide, hafnium oxide, and hafnium silicates in dilute hydrofluoric acid solutions J. Mater. Res. 19 1149–56

- [59] Dekker J, Kolari K and Puurunen R L 2006 Inductively coupled plasma etching of amorphous Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> mask layers grown by atomic layer deposition *J. Vac. Sci. Technol.* B 24 2350

- [60] Min K S, Park B J, Kim S W, Kang S K, Yeom G Y, Heo S H, Kang C Y and Hwang H S 2008 Selective etching og HfO<sub>2</sub> by using inductively-coupledAr/C<sub>4</sub>F<sub>8</sub> plasmas and the removal of etch residue on Si by using an O<sub>2</sub> plasma treatment J. Korean Phys. Soc. 53 1675–9

- [61] Kim D-P, Yeo J-W and Kim C-I 2004 Etching properties of Al<sub>2</sub>O<sub>3</sub> films in inductively coupled plasma *Thin Solid Films* 459 122-6

- [62] Firek P, Szmidt J, Nowakowska-Langier K and Zdunek K 2009 Electric characterization and selective etching of aluminum oxide *Plasma Process. Polym.* 6 S840–3

- [63] Wang L et al 2013 One-dimensional electrical contact to a twodimensional material Science 342 614–7

- [64] Chu T and Chen Z 2014 Understanding the electrical impact of edge contacts in few-layer graphene ACS Nano 8 3584–9

- [65] Guimarães M H D, Gao H, Han Y, Kang K, Xie S, Kim C-J, Muller D A, Ralph D C and Park J 2016 Atomically thin ohmic edge contacts between two-dimensional materials ACS Nano 10 6392–9

- [66] Zhang Y, Yang R, George S M and Lee Y C 2011 In-situ inspection of cracking in atomic-layer-deposited barrier films on surface and in buried structures Thin Solid Films 520 251-7

- [67] Mayorov A S et al 2011 Micrometer-scale ballistic transport in encapsulated graphene at room temperature Nano Lett. 11 2396–9

- [68] Nagashio K, Yamashita T, Fujita J, Nishimura T, Kita K and Toriumi A 2010 Impacts of graphene/SiO<sub>2</sub> interaction on FET mobility and Raman spectra in mechanically exfoliated graphene films *Electron Devices Meet. (IEDM)*, 2010 IEEE Int. no. 11793342

- [69] Unarunotai S, Murata Y, Chialvo C E, Kim H, MacLaren S, Mason N, Petrov I and Rogers J A 2009 Transfer of graphene layers grown on SiC wafers to other substrates and their integration into field effect transistors *Appl. Phys. Lett.* 95 202101

- [70] Xu H, Chen Y, Zhang J and Zhang H 2012 Investigating the mechanism of hysteresis effect in graphene electrical field device fabricated on SiO<sub>2</sub> substrates using Raman spectroscopy Small 8 2833–40

- [71] Wang X, Zhi L and Mu K 2008 Transparent, conductive graphene electrodes for dye-sensitized solar cells *Nano Lett*. 8 323–7

- [72] Pang S, Hernandez Y, Feng X and Müllen K 2011 Graphene as transparent electrode material for organic electronics Adv. Mater. 23 2779–95

- [73] Zhang D W, Li X D, Li H B, Chen S, Sun Z, Yin X J and Huang S M 2011 Graphene-based counter electrode for dyesensitized solar cells *Carbon* 49 5382–8

- [74] Burke A, Ito S, Snaith H, Bach U, Kwiatkowski J and Grätzel M 2008 The function of a TiO<sub>2</sub> compact layer in dye-sensitized solar cells incorporating 'planar' organic dyes *Nano Lett.* 8 977–81

- [75] Sanders S et al 2015 Engineering high charge transfer n-doping of graphene electrodes and its application to organic electronics Nanoscale 7 13135–42

- [76] Kidambi P R, Weijtens C, Robertson J, Hofmann S and Meyer J 2015 Multifunctional oxides for integrated manufacturing of efficient graphene electrodes for organic electronics Appl. Phys. Lett. 106 063304